Modul 2 : Laporan Akhir 1

PERCOBAAN 1

1. Jurnal[Kembali]

2. Alat dan Bahan[Kembali]

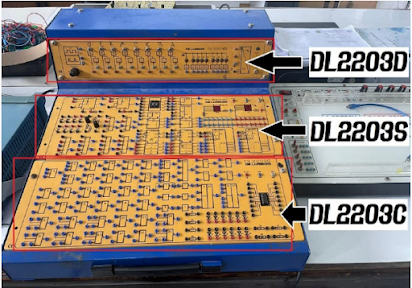

- Panel DL 2203C.

- Panel DL 2203D.

- Panel DL 2203S.

Modul D'Lorenzo Modul D'Lorenzo berfungsi sebagai alat untuk membuat rangkaian yang diperlukan untuk melakukan percobaan. Masing-masing Panel meiliki a - Jumper.

Jumper Jumper berfungsi untuk menghubungkan bagian-bagiaan yang terdsedia pada panel-panel pada modul D'Lorenzo sehingga rangkaian pada percobaan dapat terangkai.

2.1 Alat dan Bahan (Proteus)

- Power DC

- Logicprobe

3. Rangkaian

Simulasi[Kembali]

4. Prinsip Kerja Rangkaian[Kembali]

Prinsip kerja dari rangkaian ini ialah ketika B0, B1, B2, B3, B4, B5, B6 pada modul D,Lorenzo diatur kondisinya (keatas bernilai satu dan kebawah bernilai nol) akan mempengaruhi keluaran pada H7, H6, H4, dan H3 yang ketika keluarannya bernilai satu lampu indikator akan hidup sedangkan ketika bernilai nol lampu indikator akan mati. Pada rangkaian percobaan 1 terdapat 2 flip-flop yang mengikuti prinsip kerja dari D flip-flop dan J-K flip flop dimana ketika masukan pada pin set (B1) dan pin reset (B0) bernilai 1 maka keluaran pada D flip flop akan bergantung pada masukan pada pin D (B5) dan keluaran pada J-K flip flop akan bergantung pada masukan pin J (B4) dan pin K (B5) dengan syarat clock kedua flip-flop (B3 dan B6) di hidup-matikan. Masukan pada B0 sampai B6 akan diatur nilainya pada jurnal

5. Video Rangkaian[Kembali]

6. Analisa[Kembali]

1.Bagaimana jika B0 dan B1 sama-sama diberi logika 0, apa yang terjadi pada rangkaian ?

Ketika B0 dan B1 diberi logika 0, pin set serta pin reset pada D flip flop dan J-K flip flop otomatis akan medapatkan masukan bernilai nol. Pin set dan pin reser kedua flip flop bersifat aktif rendah, artiya ketika diberi masukan bernilai nol kedua pin ini akan aktif. Ketika pin set dan pin reset aktif, flip flop akan mengalami kondisi terlarang dimana keluaran Q dan Q' pada kedaua flip flop memberikan keluaran bernilai satu akibatnya lampu pada H2, H3, H7, dan H6 akan hidup. ketika flip flop mengalami kondisi terlarang inputan pada B2, B3, B4, B5 dan B6 tidak akan mempengaruhi keluaran dari flip flop.

Ketika B0 dan B1 diberi logika 0, pin set serta pin reset pada D flip flop dan J-K flip flop otomatis akan medapatkan masukan bernilai nol. Pin set dan pin reser kedua flip flop bersifat aktif rendah, artiya ketika diberi masukan bernilai nol kedua pin ini akan aktif. Ketika pin set dan pin reset aktif, flip flop akan mengalami kondisi terlarang dimana keluaran Q dan Q' pada kedaua flip flop memberikan keluaran bernilai satu akibatnya lampu pada H2, H3, H7, dan H6 akan hidup. ketika flip flop mengalami kondisi terlarang inputan pada B2, B3, B4, B5 dan B6 tidak akan mempengaruhi keluaran dari flip flop.

2. Bagaimana jika B3 diputuskan atau tidak dihubungkan pada rangkaian apa yang terjadi pada rangkaian ?

Memutuskan B3 tidak akan mempengaruhi keluaran pada D flip flop karena secara hubungan, B3 tidak tersambung dengan pin pada D flip flop. Pemutusan B3 akan mempengaruhi keluaran yang melibatkan masukan clock pada J-k flip flop, artinya kondisi terlarang, asinkronus reset, dan asinkronus set tidak akan terpengaruh oleh pemutusan B3. Kondisi pada J-K flip flop yang paling terpengruh dengan pemutusan B3 adalah kondisi toggle. Kondisi toggle memerlukan inputan pada B3 karena kondisi ini bersifat merubah keluaran etiap time rise ataupun time fall sesuai dengan jenis operasai clock pada flip-flop.

3.Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada flip flop !

Kondisi toggle adalah kondisi pada flip flop yang menghasilkan perubahan pada keluaran berdasarkan periode pada clock. Perubahan yang dimaksud adalah perubahan pada keluaran Q dan Q' yang bertuakr. Konsisi not change adalah kondisi pada flip flop yang mengikuti kondisi keluaran sebelumnya. Misalnya keluaran awal Q bernilai satu dan Q' bernilai nol. Kondisi not change tidak akan merubah keluaran Q bernilai nol dan Q' bernilai satu. Kondisi terlarang adalah kondisi pada flip flop yang ditandai dengan keluaran Q dan Q' sama-sama bernilai satu ataupun bernilai sama. Kondisi ini disebut terlarang karena harusnya keluaran Q dan Q' harusnya berbeda.

7. Link Download[Kembali]