Modul 4 : Laporan Akhir 1

PERCOBAAN 1

1. Jurnal[Kembali]

2. Alat dan Bahan[Kembali]

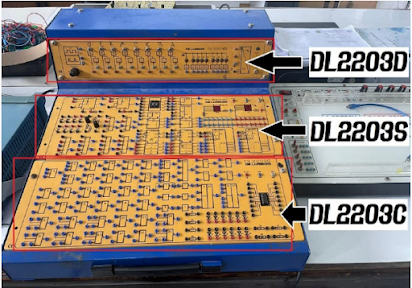

- Panel DL 2203C.

- Panel DL 2203D.

- Panel DL 2203S.

Modul D'Lorenzo Modul D'Lorenzo berfungsi sebagai alat untuk membuat rangkaian yang diperlukan untuk melakukan percobaan. Masing-masing Panel meiliki a - Jumper.

Jumper Jumper berfungsi untuk menghubungkan bagian-bagiaan yang terdsedia pada panel-panel pada modul D'Lorenzo sehingga rangkaian pada percobaan dapat terangkai.

2.1 Alat dan Bahan (Proteus)

- Power DC

- Logicprobe

- IC 74LS112

- Gerbang OR

3. Rangkaian

Simulasi[Kembali]

4. Prinsip Kerja Rangkaian[Kembali]

Rangkaian pada percobaan 1 memiliki 3 mode shift register yaitu SISO ( serial in / serial out ) , PISO ( paralel in / serial out ) , dan PIPO ( paralel in / paralel out ) . Masing- masing shift register dapat dipilih dengan cara mengatur masukan switch pada rangkaian. Untuk memilih SISO, switch 1 sampai 4 dan switch 7 diatur menjadi high dan switch 6 digunakan sebagai masukan data ke sistem. Untuk memilih PIPO switch 6 diatur don't care dan switch 7 diatur low dan switch 1 sampai 4 sebagai masukan data ke sistem dimana siwtch 1 MSB dan switch 4 LSB. Dan untuk PISO switch 6 diatur low dan switch 7 diatur high dan switch 1 sampai 4 sebagai masukan data ke sistem.

5. Video Rangkaian[Kembali]

6. Analisa[Kembali]

1.Analisa output yang dihasilkan tiap tiap kondisi

Pada kondisi 1, shift register bersifat SISO (serial in serial out) karena tampak pada keluaran H4 - H7 data keluar secara satu per satu ( ada pergeseran ) dan data masuk satu per satu. Pada kondisi 2, shift register ersifat SIPO ( serial in paralel out ) karena tampak pada keluaran data keluaran secara serentak dan lansung ( tidak ada pergeseran ) dan data masuk satu per satu. Pada kondisi 3, shift register bersifat PISO ( paralel in serial out ) karena tampak pada keluaran data keluar secara satu per satu ( ada pergeseran ) dan data masuk secara langsung. Pada kondisi 4, shift register bersifat PIPO ( paralel in paralel out) karena tampak pada keluaran data keluar secara langsung ( tidak ada pergeseran ) dan data masuk secara langsung. Pada rangkaian percobaan ini, serial in ditandai dengan switch data masuk berjumlah satu dan paralel in switch data amsuknya lebih dari satu. Untuk serial out keluarannya terdapat pergeseran data dan paralel out keluarannya langsung.

2. Jika gerbang And pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip flop, bandingkan output yang didapatkan.

Output setelah tidak ada gerbang And dan ada gerbang And adalah sama karena gerbang And ini terhubung dengan masing-masing pin CLK setiap flip flop sehingga tidak mempengaruhi keluaran dari rangkaian. Namun perubahan gerbang And ini akan mempengaruhi proses masuk data pada shift register SIPO karena pada percobaan ini data masuk ketika switch B2 fall time ( ada gerbang And ) sehingga ketika gerang And tidak ada akan terjadi perbedaan pada proses data masuk ke sistem.

7. Link Download[Kembali]